当前,生成式人工智能已引爆新一轮智能革命的发展浪潮,大算力支撑下的人工智能技术极大改变着人类的生产生活方式。可随之而来的海量参数令算力需求持续攀升,如何解决庞大的算力缺口,实现能效比的大幅提升,正在变得日益迫切。高算力、高能效芯片作为算力的具体载体,已成为驱动本轮智能革命发展的核心底座,更是推动人类社会不断发展的动力源泉。

面向传统存算分离架构制约算力提升的重大挑战,清华大学集成电路学院吴华强教授、高滨副教授聚焦忆阻器存算一体技术研究,探索实现计算机系统新范式。忆阻器存算一体技术从底层器件、电路架构和计算理论全面颠覆了冯·诺依曼传统计算架构,可实现算力和能效的跨越式提升,同时,该技术还可利用底层器件的学习特性,支持实时片上学习,赋能基于本地学习的边缘训练新场景。当前国际上的相关研究主要集中在忆阻器阵列层面的学习功能演示,然而实现全系统集成的、支持高效片上学习的忆阻器芯片仍面临较大挑战,至今还未实现,主要在于传统的反向传播训练算法所要求的高精度权重更新方式与忆阻器实际特性的适配性较差。

为解决上述难题,课题组基于存算一体计算范式,创造性提出适配忆阻器存算一体实现高效片上学习的新型通用算法和架构(STELLAR),有效实现大规模模拟型忆阻器阵列与CMOS的单片三维集成,通过算法、架构、集成方式的全流程协同创新,研制出全球首颗全系统集成的、支持高效片上学习的忆阻器存算一体芯片。该芯片包含支持完整片上学习所必需的全部电路模块,成功完成图像分类、语音识别和控制任务等多种片上增量学习功能验证,展示出高适应性、高能效、高通用性、高准确率等特点,有效强化了智能设备在实际应用场景下的学习适应能力。相同任务下,该芯片实现片上学习的能耗仅为先进工艺下专用集成电路(ASIC)系统的3%,展现出卓越的能效优势,极具满足人工智能时代高算力需求的应用潜力,为突破冯·诺依曼传统计算架构下的能效瓶颈提供了一种创新发展路径。

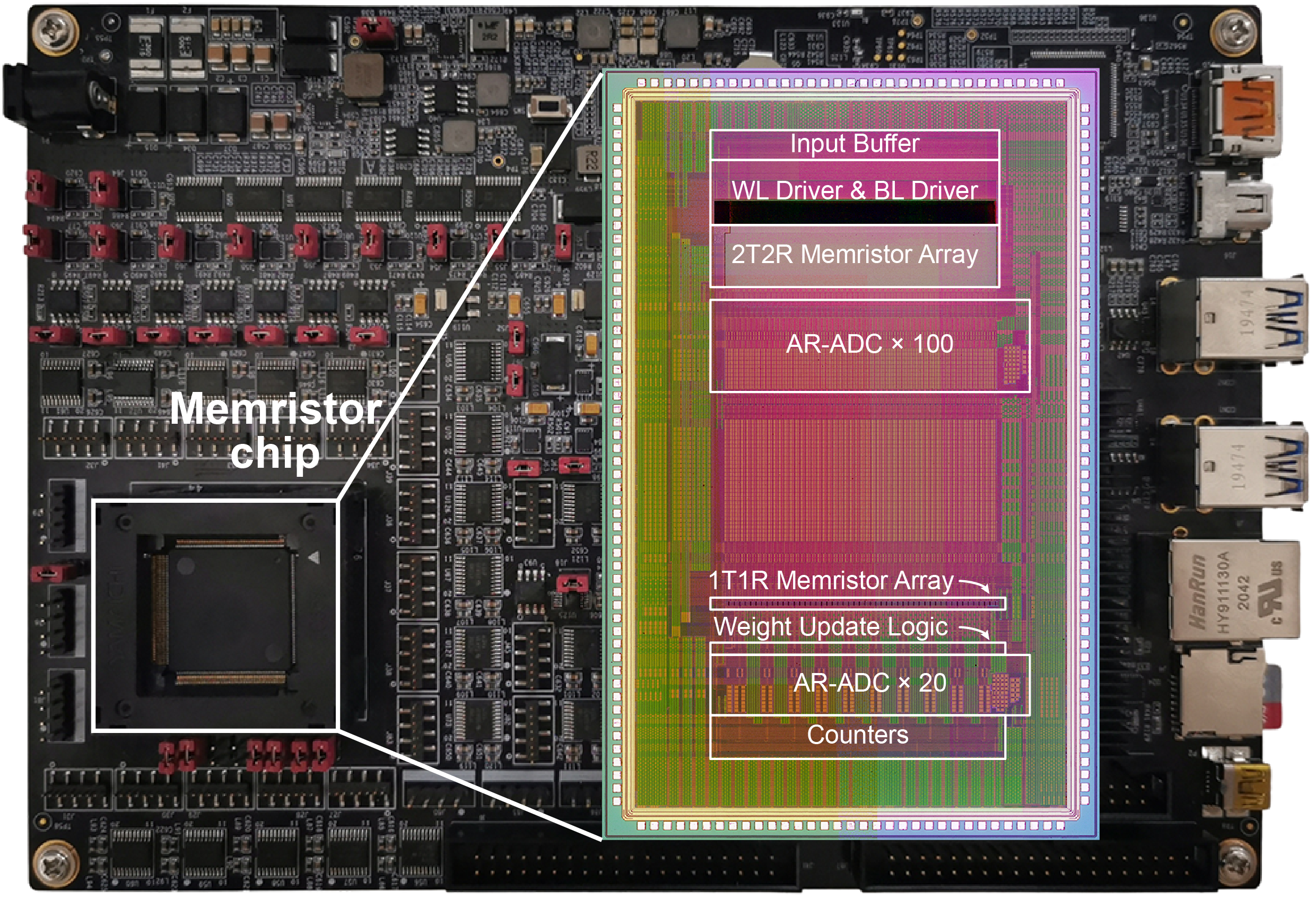

忆阻器存算一体芯片及测试系统

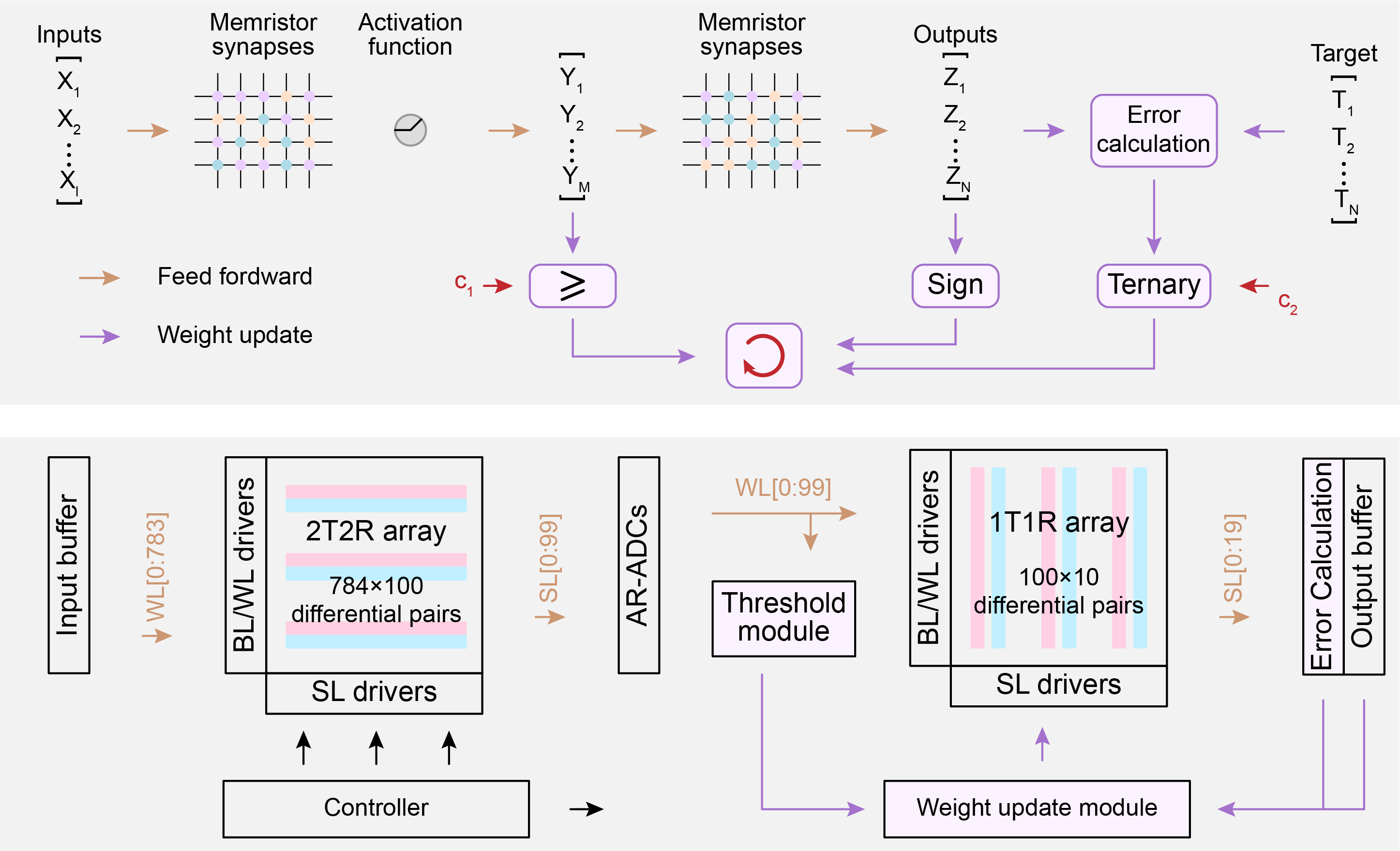

基于忆阻器存算一体实现高效片上学习的通用算法和架构

近日,该研究成果以“面向边缘学习的全集成类脑忆阻器芯片”(Edge Learning Using a Fully Integrated Neuro-Inspired Memristor Chip)为题在线发表在《科学》(Science)上。

论文通讯作者为清华大学集成电路学院高滨副教授和吴华强教授,清华大学集成电路学院博士生张文彬、博士后姚鹏为论文的共同第一作者,其他参加研究的作者包括清华大学集成电路学院钱鹤教授、唐建石副教授、伍冬副研究员、张清天助理研究员,清华大学电子系汪玉教授等。

该研究得到科技部科技创新2030“脑科学与类脑研究”重大项目、国家自然科学基金委后摩尔重大研究计划、北京集成电路高精尖中心等的支持。

论文链接:

https://www.science.org/doi/full/10.1126/science.ade3483

说明:文章来源于清华大学集成电路学院网站